Prof. Dr. Jörg Keller

# **Modul 63511**

# Einführung in die technischen und theoretischen Grundlagen der Informatik

Lehrveranstaltung

Einführung in die technische und theoretische Informatik

**LESEPROBE**

Fakultät für Mathematik und Informatik

# Kapitel 1

# Aufbau und Funktion eines Personal Computers

# Zusammenfassung

In dieser Kurseinheit werden wir in die grundlegende Struktur von Desktop-Systemen oder PCs (Personal Computer) einführen. Der Kern eines PCs besteht aus der Hauptplatine, auch Motherboard genannt, auf dem der Prozessor, Speicher, Ein-/Ausgabebausteine und -schnittstellen untergebracht sind. Wir beschäftigen uns ausführlich mit der Hauptplatine und den wichtigsten Komponenten, die auf ihr zu finden sind: das sind der Mikroprozessor als "Gehirn" eines Mikrorechners und der Chipsatz, der die Steuerung der übrigen Komponenten – insbesondere des Hauptspeichers und der Peripheriemodule – vornimmt und sie mit dem Prozessor verbindet. Der Aufbau eines Prozessors und seiner Komponenten wird erst in der Kurseinheit 2 ausführlich behandelt. Dabei beschränken wir uns auf Platinen und Bausteine, die für den Einsatz in Desktop-PCs vorgesehen sind. Auf Exemplare, die ihren Einsatz in Servern, Workstations oder Laptops finden, können wir hier aus Platzgründen nicht eingehen.

# Lernziele

In dieser Kurseinheit werden Sie sich mit den folgenden Themen befassen:

- dem Aufbau und den wichtigsten Komponenten eines modernen (Desktop-)PCs,

- dem Aufbau und die Funktion der Chipsätze, die in diesen PCs Verwendung finden,

- den gebräuchlichen Speichermodulen und ihren wichtigsten Parametern,

- die Massenspeicher-Medien, wie Festplatte, CD-ROM und DVD,

- der Funktion der wichtigsten Ein-/Ausgabegeräte, also Tastatur, Maus und Monitor.

## 1.1 Einführung

#### 1.1.1 Aktuelle Computersysteme

In diesem Kapitel soll ein kurzer Überblick über aktuelle Computersysteme gegeben werden. Zunächst stellen wir die verschiedenen Arten von Computern vor. Dann betrachten wir am Beispiel von *Desktop*–Systemen deren internen Aufbau, der vor allem durch den Chipsatz geprägt wird. Danach werden die aktuellen Desktop–Prozessoren der beiden führenden Hersteller AMD und Intel vorgestellt und miteinander verglichen. Im Weiteren beschreiben wir die Funktionsprinzipien der aktuellen Speichermodule sowie Ein– und Ausgabeschnittstellen. Schließlich gehen wir auch auf die Bedeutung von Graphikadaptern ein und geben einen Ausblick auf die künftige Entwicklung.

Die Entwicklung neuer Prozessorarchitekturen und Computersysteme ist rasant. Die Chiphersteller vermelden fast täglich neue technologische und architektonische Verbesserungen ihrer Produkte. Daher fällt es natürlich auch schwer, einen aktuellen Schnappschuss der Entwicklung wiederzugeben – zumal dieser dann nach kurzer Zeit wieder veraltet ist. Trotzdem wollen wir im Folgenden versuchen, den Stand im Herbst 2009 zu erfassen.

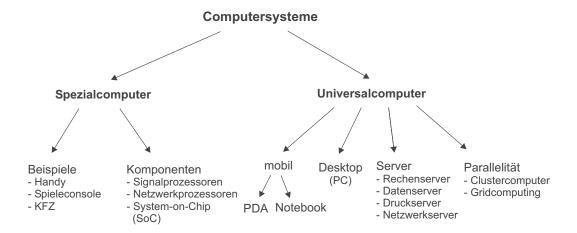

#### 1.1.2 Arten von Computern

Obwohl es uns meist nicht bewusst ist, sind wir heutzutage von einer Vielzahl verschiedenster Computersystemen umgeben. Die meisten Computer, die wir täglich nutzen, sind nämlich in Gebrauchsgegenständen eingebaut und führen dort Spezialaufgaben aus. So bietet uns beispielsweise ein modernes Mobiltelefon ("Handy") die Möglichkeit, Telefonnummern zu verwalten, elektronische Textnachrichten (SMS) zu versenden, Musik abzuspielen oder sogar Bilder aufzunehmen. Ahnliche Spezialcomputer findet man in Geräten der Unterhaltungselektronik (z.B. CD-, DVD-, Video-Recordern, Satelliten-TV-Empfängern), Haushaltstechnik (z.B. Wasch- und Spülmaschinen, Trockner, Mikrowelle), Kommunikationstechnik (z.B. Telefon- und Fax-Geräte) und auch immer mehr in der Kfz-Technik (z.B. intelligentes Motormanagement, Antiblockier- und Stabilisierungssysteme). Diese Spezialcomputer oder so genannten eingebetteten Systeme (Embedded Systems) werden als Bestandteile größerer Systeme kaum als Computer wahrgenommen. Sie müssen jedoch ein weites Leistungsspektrum abdecken und insbesondere bei Audio- und Videoanwendungen bei minimalem Energiebedarf Supercomputer-Leistungen erbringen. Solche Systeme basieren meist auf Prozessoren, die für bestimmte Aufgaben optimiert wurden (z.B. Mikrocontroller, Signal- oder Netzwerkprozessoren). Aufgrund der immensen Fortschritte der Mikroelektronik ist es sogar möglich, Prozessorkerne zusammen mit zusätzlich benötigten digitalen Schaltelementen auf einem einzigen Chip zu realisieren (System on a Chip – SoC).

Neben diesen eingebetteten Systemen gibt es auch die so genannten *Universal-computer*. Gemeinsames Kennzeichen dieser Computersysteme ist, dass sie ein breites Spektrum von Funktionen bereitstellen, die durch dynamisches Laden entsprechender Programme implementiert werden. Neben Standardprogrammen für Büroanwendungen (z.B. Schreib- und Kalkulationsprogramme) gibt

1.1. Einführung

es für jede nur erdenkliche Anwendung geeignete Software, die den Universalcomputer in ein anwendungsspezifisches Werkzeug verwandelt (z.B. Entwurfsund Konstruktionsprogramme, Reiseplaner, Simulatoren usw.).

Derartige Universalcomputer unterscheiden sich hinsichtlich der Größe und Leistungsfähigkeit. Die kleinsten und leistungsschwächsten Universalcomputer sind kompakte und leichte Taschencomputer (Handheld Computer), die auch als PDAs (Personal Digital Assistant) bekannt sind. Sie verfügen über einen nichtflüchtigen Speicher, der auch im stromlosen Zustand die gespeicherten Informationen behält. PDAs können mit einem Stift über einen kleinen berührungsempfindlichen Bildschirm (Touch Screen) bedient werden und sind sogar in der Lage, handschriftliche Eingaben zu verarbeiten.

Notebooks sind ebenfalls portable Computer. Sie haben im Vergleich zu PDAs größere Bildschirme, eine richtige Tastatur und ein Sensorfeld, das als Zeigeinstrument (Maus-Ersatz) dient. Sie verfügen auch über deutlich größere Speicherkapazitäten (sowohl bzgl. Haupt- als auch Festplattenspeicher) und werden immer häufiger als Alternative zu ortsfesten Desktop-Computern verwendet, da sie diesen insbesondere bei Büro- und Kommunikationsanwendungen ebenbürtig sind. Um eine möglichst lange vom Stromnetz unabhängige Betriebsdauer zu erreichen, werden in Notebooks energiesparende Prozessoren eingesetzt.

Desktop-Computer oder PCs (Personal Computer) sind Notebooks vor allem bzgl. der Rechen- und Graphikleistung überlegen. Neben den typischen Büroanwendungen werden sie zum rechnergestützten Entwurf (Computer Aided Design – CAD), für Simulationen oder auch für Computerspiele eingesetzt. Die dazu verwendeten Prozessoren und Graphikadapter produzieren hohe Wärmeleistungen (jeweils in der Größenordnung von ca. 100 Watt), die durch große Kühlkörper und Lüfter abgeführt werden müssen.

Weitere ortsfeste Computersysteme sind die so genannten Server. Im Gegensatz zu den Desktops sind sie nicht einem einzelnen Benutzer zugeordnet. Da sie Dienstleistungen für viele über ein Netzwerk angekoppelte Desktops oder Notebooks liefern, verfügen sie über eine sehr hohe Rechenleistung (Compute Server), große fehlertolerierende und schnell zugreifbare Festplattensysteme<sup>1</sup> (File Server, Video-Stream Server), einen oder mehrere Hochleistungsdrucker (Print Server) oder mehrere schnelle Netzwerkverbindungen (Firewall, Gateway).

Server-Systeme werden in der Regel nicht als Arbeitsplatzrechner genutzt, d.h. sie verfügen weder über leistungsfähige Graphikadapter noch über Peripheriegeräte zur direkten Nutzung (Monitor, Tastatur oder Maus).

Um sehr rechenintensive Anwendungen zu beschleunigen, kann man mehrere Compute Server zu einem so genannten Cluster-Computer zusammenschalten. Im einfachsten Fall, werden die einzelnen Server-Systeme über einen Switch mit Fast- oder Gigabit-Ethernet zusammengeschaltet. Über diese Verbindungen können dann die einzelnen Compute Server Daten untereinander austauschen und durch gleichzeitige (parallele) Ausführung von Teilaufgaben die Gesamtaufgabe in kürzerer Zeit lösen. Die maximal erreichbare Beschleunigung hängt dabei von der Körnigkeit (Granularity) der parallelen Programme ab. Cluster-

<sup>&</sup>lt;sup>1</sup>Meist so genannte RAID (Redundant Array of Independent Disks).

Abbildung 1.1: Übersicht über die verschiedenen Arten von Computersystemen.

Computer sind vor allem für grobkörnige (coarse grained) Parallelität geeignet. Hier sind die Teilaufgaben zwar sehr rechenintensiv, die einzelnen Programmteile müssen jedoch nur geringe Datenmengen untereinander austauschen.

Je feinkörniger (fine grained) ein paralleles Programm ist, desto höher sind die Anforderungen an das dem Cluster zu Grunde liegende Netzwerk. Um eine hohe Beschleunigung der feinkörnigen Programme zu erreichen, muss die Netzwerkverbindung sowohl eine hohe Datenrate bereitstellen als auch möglichst geringe Latenzzeiten aufweisen.

Betrachtet man die über das Internet verbundenen Computersysteme, so erkennt man, dass diese ähnlich wie bei einem Cluster-Computer organisiert sind. Auch hier kann jeder Netzwerkknoten mit jedem beliebigen anderen Knoten Daten (oder Programme) austauschen. Aufgrund der komplexen Vermittlungsstrategien des Internetprotokolls (IP) muss man allerdings mit höheren Latenzzeiten und geringeren Datenraten rechnen, d.h. man ist auf grobkörnige Parallelität beschränkt. Trotzdem hält dieser "weltweite" Cluster-Computer extrem hohe Rechenleistungen bereit, da die angeschlossenen Desktop-Systeme im Mittel nur zu ca. 10% ausgelastet sind. Um diese immense brachliegende Rechenleistung verfügbar zu machen, entstanden in den letzten Jahren zahlreiche Forschungsprojekte zum so genannten Grid-Computing.

Der Name Grid wird in Analogie zum Power Grid verwendet, bei dem es um eine möglichst effektive Nutzung der in Kraftwerken erzeugten elektrischen Energie geht. Die Kernidee des Grid-Computings besteht darin, auf jedem Grid-Knoten einen permanenten Zusatzprozess laufen zu lassen, über den dann die Leerlaufzeiten des betreffenden Desktop-Computers für das Grid nutzbar gemacht werden können. Diese Software wird als Grid-Middleware bezeichnet. Die am weitesten verbreitete Grid-Middleware ist das Globus-Toolkit. Neben der Grid-Middleware wird auch ein so genannter Grid-Broker benötigt, der für jeden eingehenden Benutzerauftrag (Job) geeignete Computerkapazitäten (Resourcen) sucht und der nach der Bearbeitung die Ergebnisse an den Benutzer weiterleitet. In Analogie zum World Wide Web (WWW) spricht man beim Grid-Computing auch von einem World Wide Grid (WWG). Es bleibt abzuwarten, ob sich dieser Ansatz genauso revolutionär entwickelt wie das WWW.

1.1. Einführung 5

Nach dem Kursüberblick im Abschnitt 1.1 über die verschiedenen Arten moderner Computersysteme werden wir im weiteren Verlauf der Kurseinheit den Aufbau von Desktop—Systemen genauer betrachten und anschließend die Architektur der aktuellen Desktop—Prozessoren von AMD und Intel vorstellen. Als verbindenden Komponenten kommt den Chipsätzen eine besondere Bedeutung zu.

# 1.2 Komponenten eines Personal Computers

Ein PC (Personal Computer) ist ein Rechner, der – wie der Name es nahe legt

– nur von einer Person (oder wenigen Personen) genutzt wird. Im Gegensatz zu zentralen (Groß–)Rechnern steht somit beim PC dem Benutzer die gesamte Rechenleistung exklusiv zur Verfügung. Da ein PC am Arbeitsplatz des Benutzers steht, wird er auch als Desktop PC bezeichnet<sup>2</sup>. Ein Desktop PC verfügt über alle Hard– und Software–Komponenten, die zur interaktiven Arbeit mit lokalen Anwendungen – wie z.B. Textverarbeitung, Tabellenkalkulation, Programmierung usw. – nötig sind. Darüber hinaus verfügen alle modernen PCs über Netzwerkschnittstellen, um mit anderen Rechnern Daten auszutauschen oder auf zentrale Dateiserver bzw. auf das Internet zuzugreifen. Leistungsfähige PCs, die über eine solche Netzwerkschnittstelle und besonders schnelle Graphiksysteme verfügen, werden auch als Workstations bezeichnet. Ein Server ist ein Rechner, der Betriebsmittel, wie Dateisysteme, Drucker, Internetverbindungen usw., für andere Rechner bereitstellt. Ein Notebook PC oder Laptop PC fasst alle Komponenten eines Personal Computers auf kleinstem Raum zusammen.

PCs.<sup>3</sup>

Während bei mobilen Systemen alle Komponenten in einem Gerät integriert sind, können bei stationären PCs die einzelnen Komponenten – wie die Systemeinheit mit ihren Schnittstellen sowie die Ein– und Ausgabegeräte – unterschieden werden. Die wichtigsten Eingabegeräte sind Tastatur und Maus, die wichtigsten Ausgabegeräte Monitor und Drucker.

Da diese mit Akkumulatoren (Akkus) betrieben werden können, sind sie portabel. Eine weitere Miniaturisierung findet man bei *Handheld PCs* oder *Palmtop*

Die Systemeinheit besteht aus einem Gehäuse mit Netzteil und den Schnittstellen zur Peripherie. Die Abbildung 1.2 gibt einen ersten, groben Überblick über die grundlegenden Komponenten innerhalb der Systemeinheit eines PCs:

- Hauptplatine (Motherboard, Mainboard) mit integrierten Schnittstellen,

- Schnittstellenkarten für PCI-Express (Peripheral Component Interconnect) oder andere Bussysteme,

- Festplattenlaufwerk(e) (Hard-Disk Drive HDD),

- Diskettenlaufwerk(e), die jedoch kaum noch zu finden sind,

- CD-ROM- bzw. DVD-Laufwerke,

- Monitor, Tastatur und Maus.

Auf der Hauptplatine befinden sich der Prozessor, der Hauptspeicher und Steckplätze für Bussysteme mit unterschiedlicher Geschwindigkeit. Über speziell auf

Desktop-PC

Server

Hauptplatine

<sup>&</sup>lt;sup>2</sup> Desktop: Schreibtisch-Oberfläche

<sup>&</sup>lt;sup>3</sup> Notebook: Notizbuch, Lap: Schoß, Palm: Handfläche

Abbildung 1.2: Der Aufbau eines PCs.

die Prozessoren abgestimmte Chipsätze werden die genormten Peripheriebus—Signale aus den Prozessorbus—Signalen abgeleitet. An diese Busse können über Steckkontakte Schnittstellenkarten angeschlossen werden, die dann standardisierte Schnittstellen für Massenspeicher oder Peripheriegeräte bereitstellen. Auf den meisten aktuellen Hauptplatinen sind auch bereits einfache parallele und serielle Standardschnittstellen sowie meist auch eine ganze Anzahl von USB—Schnittstellen (*Universal Serial Bus*) integriert. Ebenso findet man meist auch eine (S)ATA—Schnittstelle in paralleler oder serieller Form ((*Serial*) Advanced Technology Attachment) für magnetomotorische und optische Massenspeicher mit einem integriertem Laufwerkscontroller (*Integrated Device Electronic*—IDE). Neben Controllern für Laufwerke ist bei heutigen Hauptplatinen meist auch schon eine Ethernet—Netzwerkschnittstelle zur Integration des PCs in ein lokales Netzwerk vorhanden.

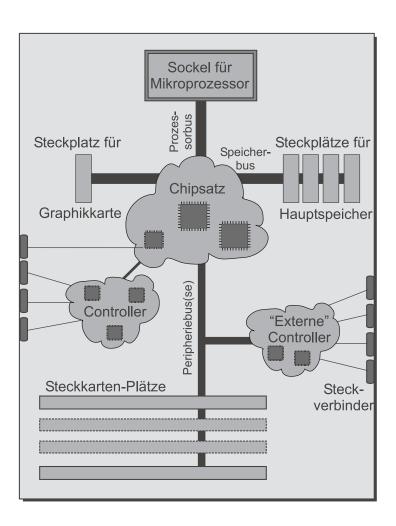

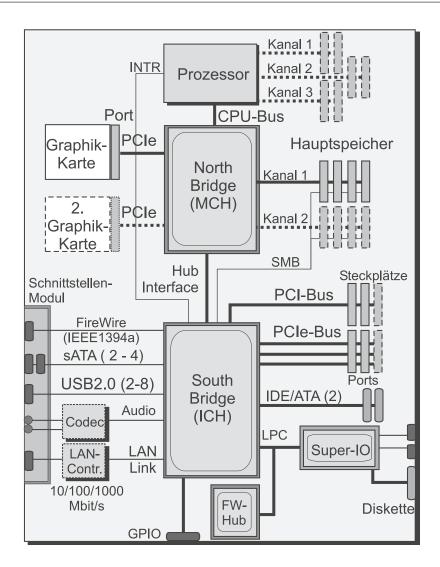

Zunächst lassen wir bei unserer Betrachtung die externen Geräte eines PCs außer Betracht und behandeln ausschließlich den im PC "eingebetteten" Mikrorechner, der im Wesentlichen als Steckkartensystem realisiert ist. Abbildung 1.3 zeigt schematisch die wesentlichen Komponenten, die sich auf der Hauptplatine befinden (vgl. auch Abbildung 1.4):

- der Mikroprozessor, auch CPU (*Central Processing Unit*) genannt, der in einem speziellen Sockel eingesteckt wird,

- Module des Hauptspeichers, für die eine unterschiedliche Anzahl von Steckplätzen vorhanden sind,

- ein Steckplatz für eine Graphikkarte,

- den Peripherie- oder Erweiterungsbussen mit Steckplätzen zur Aufnahme verschiedener Steckkarten (Erweiterungskarten, Add-On Cards),

- der so genannte **Chipsatz**, eine Sammlung von mehreren hochintegrierten Bausteinen, die insbesondere die Verbindung der eben genannten Komponenten und die Unterstützung der Kommunikation zwischen ihnen zur Aufgabe haben; daneben enthalten sie aber noch eine ganze Reihe von Steuermodulen zum Anschluss interner und externer Geräte;

- verschiedene Steuer- und Schnittstellenbausteine unterschiedlicher Komplexität, die direkt an den Bausteinen des Chipsatzes oder am Peripheriebus angeschlossen sind und z.T. über Steckverbinder mit externen Komponenten gekoppelt werden.

Abbildung 1.3: Der prinzipielle Aufbau einer Hauptplatine.

Die erwähnten Sockel und Steckplätze sind in der Regel exakt auf spezielle Bausteine, also Prozessoren, Speichermodule und Graphikkarten, abgestimmt. Hochleistungs-PCs enthalten darüber hinaus auch Sockel und Steckplätze für

#### Chipsatz

mehr als einen Prozessor bzw. zwei Graphikkarten. Die in den Chipsätzen integrierten Steuer- und Schnittstellenmodule, aber auch die oben erwähnten "externen" Steuer- und Schnittstellenbausteine werden typischerweise Controller Controller genannt. Zu den Erweiterungskarten gehören insbesondere Graphikkarten, Audiokarten (Soundcards) und Netzwerkkarten (LAN Cards). Der Fortschritt der Integrationstechnik ermöglicht es aber, immer mehr von diesen Erweiterungen direkt auf der Hauptplatine unterbringen, z.B. den Controller für den Netzwerkanschluss und die Audioverarbeitung. Andererseits kann der PC durch Erweiterungskarten wieder mit "Altlast"-Schnittstellen (Legacy) ausgerüstet werden, die in den letzten Jahren nicht mehr zum Standardumfang eines PCs gehören und daher nicht mehr vom Chipsatz zur Verfügung gestellt werden, wie zum Beispiel die früher weit verbreiteten parallelen und seriellen Schnittstellen<sup>4</sup>. Ein Steckverbinder-Modul, das auf der Hauptplatine zur Gehäuserückwand zeigt, liefert die Anschlüsse für eine ganze Reihe von Standard-Ein-/Ausgabegeräten, wie z.B. Tastatur, Maus, Netzwerk, Lautsprecher usw. (Auf dieses Modul werden wir weiter unten eingehen.) Über eine Reihe von Steckern können die oben erwähnten Massenspeicher angeschlossen werden, wobei Flachbandkabel mit mehr oder weniger Kupferadern verwendet werden.

In dieser Kurseinheit werden wir uns ausschließlich mit der Hauptplatine eines PCs und ihren Komponenten beschäftigen. Nicht behandelt werden der mechanische Aufbau eines PCs, die verschiedenen Ausprägungen von gebräuchlichen Hauptplatinen, Sockel für Prozessor und Chipsätze, Fragen der Kühlung und Lüftung, Steckverbinder, Netzteile und Spannungsversorgung, Überwachung von wichtigen Parametern (Temperatur, Spannung usw.)

Die im PC-Bereich eingesetzten Mikroprozessoren werden als **x86-kompatible** Prozessoren bezeichnet, da sie sich auf den ersten 16-Bit-Prozessor von Intel, den 8086, aus dem Jahr 1979 zurückführen lassen.<sup>5</sup> Über die Leistungsfähig- x86-Prozessor keit der x86-Prozessoren entscheidet nicht zuletzt die komplexe virtuelle Speicherverwaltung und ihre Unterstützung durch die Speicherverwaltungseinheit (Memory Management Unit – MMU). Selbst eine oberflächliche Beschreibung MMU der virtuellen Speicherverwaltung und ihrer vielfältigen Funktionen würde den Rahmen dieser Kurseinheit sprengen. Wir werden dieses Thema daher erst in Kurseinheit 3 behandeln.

<sup>&</sup>lt;sup>4</sup>Diese waren früher unter den Bezeichnungen Centronics- und V.24-Schnittstellen be-

<sup>&</sup>lt;sup>5</sup>Über diese Prozessoren werden Sie in Kurseinheit 2 eine Reihe von Details erfahren und die Hauptkomponenten kennen lernen.

## 1.3 Hauptplatine und ihre Komponenten

#### 1.3.1 Hauptplatine

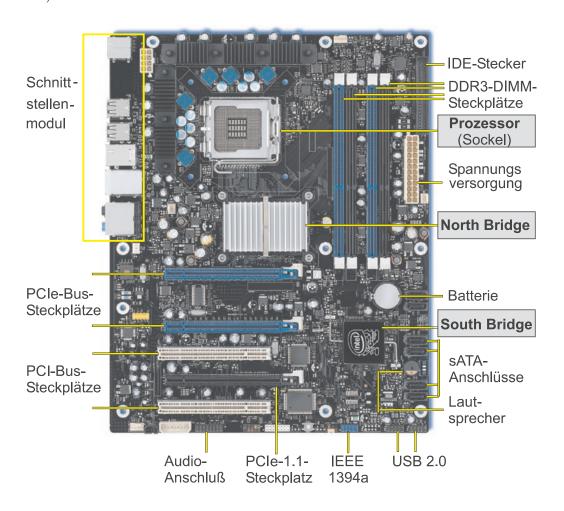

In Abbildung 1.4 ist exemplarisch eine moderne Hauptplatine für den Intel-Prozessor Core 2 gezeigt. Die in der Abbildung dargestellten Komponenten sind Gegenstand dieser und z.T. auch der folgenden Kurseinheiten.

Um Ihnen eine grobe Vorstellung von der Größe einer Hauptplatine zu geben, seien hier nur die Maße einer typischen Platine für den Desktop-Bereich gegeben (vgl. Abbildung 1.4). Ihre "genormte" Größe wird als **ATX-Formfaktor** bezeichnet und belegt die folgende Rechteckfläche:  $9.6 \times 12 \text{ Zoll}^2 = 24.4 \times 30.5 \text{ cm}^2$ . (Sie ist damit nur wenig größer als eine DIN-A4-Seite mit  $21.0 \times 29.7 \text{ cm}^2$ .)

Abbildung 1.4: Photo einer Hauptplatine (Intel Desktop Board DX48BT2).

Die Hauptplatine eines PCs (ebenso wie seine Einsteckkarten) enthielten noch vor etwas mehr als zwei Jahrzehnten Dutzende von integrierten Bausteinen (*Integrated Circuits* – ICs). Die rasante Entwicklung der Höchstintegrationstechnik (*Very Large Scale Integration* – VLSI) ermöglichte es seitdem, immer mehr Komponenten auf dem Prozessorchip selbst bzw. in sehr wenigen "Hilfs-

gungsleistungen.

bausteinen" unterzubringen. Die wichtigsten dieser Bausteine, die zum Aufbau eines PCs benötigt werden und auf der Hauptplatine Platz finden, werden zusammenfassend als Chipsatz (Chipset) bezeichnet. Der erste dieser Chipsätze Chipsatz wurde im Jahre 1988 von der Firma Chips and Technologies auf den Markt gebracht. Seither bieten die Prozessorhersteller (vor allem AMD und Intel) sowie auf die Entwicklung von Chipsätzen spezialisierte Firmen kurz nach dem Erscheinen eines neuen Prozessors auch die dazu passenden Chipsätze an.

Ein Chipsatz besteht meist aus ein bis drei Chips, die benötigt werden, um den Prozessor mit dem Speichersystem und Ein-/Ausgabebussen zu koppeln. Da diese drei Haupteinheiten mit unterschiedlichen Geschwindigkeiten arbeiten, benötigt man Brückenbausteine (Bridges), welche die vorhandenen Geschwin- Brückenbaustein digkeitsunterschiede ausgleichen und für einen optimalen Datenaustausch zwischen den Komponenten sorgen. Die Brückenbausteine müssen auf die Zeitsignale (Timing) des Prozessors abgestimmt werden. Die im PC eingesetzten Bussysteme und Schnittstellen unterscheiden sich sehr stark in der Anzahl der Daten- und Adresssignale, der Taktfrequenzen und der verwendeten Spannungspegel sowie der zugrunde liegenden Busprotokolle. Aufgabe der Brückenbausteine ist insbesondere die elektrisch/physikalische Anpassung der verschie-

Der Chipsatz hat also großen Einfluss auf die Leistungsfähigkeit eines Computersystems und muss daher optimal auf den eingesetzten Prozessor und die verwendeten Speicher-/Bustypen zugeschnitten sein. Die Bausteine des Chipsatzes übernehmen im eigentlichen Sinne die Steuerung des Systems.<sup>6</sup> Obwohl ein Chipsatz für eine bestimmte Prozessorfamilie entwickelt wird, kann er meist auch eine Vielzahl kompatibler Prozessoren unterstützen.

denen Bussignale sowie die Berücksichtigung der unterschiedlichen Übertra-

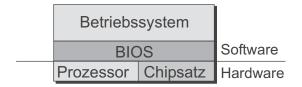

Chipsätze verfügen über z.T. sehr unterschiedliche Komponenten, Anschlüsse, Register und Funktionen. Es ist Aufgabe des sog. BIOS (Basic Input/Output System), diese Unterschiede vor dem Betriebssystem zu "verstecken", das meist BIOS für viele Prozessortypen und Familien einsetzbar sein muss. Das BIOS ermöglicht dem Betriebssystem und den darunter laufenden Anwendungsprogrammen den Zugriff auf die Hardware-Komponenten. Dazu muss es genaue Kenntnisse über den Aufbau der Hauptplatine, die Anzahl der Steckplätze sowie die verwendeten Bausteine und Komponenten besitzen. Als Beispiele seien hier nur der Zugriff auf die Plattenlaufwerke und die Abfrage der Tastatur genannt. Abbildung 1.5 zeigt die Lage des BIOS zwischen dem Betriebssystem und der Hardware, im Wesentlichen repräsentiert durch den Prozessor und den Chipsatz. Als wesentliche Aufgaben des BIOS seien hier aufgeführt:

• Ausführung eines PC-Selbsttests, der automatisch nach dem Einschal-

<sup>&</sup>lt;sup>6</sup>Auf die speziellen Komponenten zur Steuerung und Überwachung der Versorgungsspannung, der Verlustleistung, der eingesetzten Lüfter und bestimmter physikalischer Größen und Einheiten (System-/Power-/Takt-"Management") können wir aus Platzgründen leider nicht eingehen.

Abbildung 1.5: Das BIOS zwischen Betriebssystem und Hardware-Bausteinen.

ten des Systems aufgerufen wird (*Power-On Selftest –* POST). Dadurch werden z.B. die Größe des Hauptspeichers ermittelt und ein Test seiner Speicherzellen durchgeführt.

- Konfiguration der auf der Hauptplatine oder in den Steckplätzen eingesetzten Komponenten, insbesondere der am PCI- bzw. PCIe-Bus angeschlossenen Geräte.

- Ausführung eines Setup-Programms, durch das der Anwender BIOS-Daten ändern und Einfluss auf den Systembetrieb nehmen kann. Als Beispiel sei die manuelle Zuweisung von Interrupt-Kanälen zu bestimmten Komponenten genannt.

Abbildung 1.6 zeigt das Blockschaltbild einer Platine und die Lage und Verbindungen der Bausteine des Chipsatzes<sup>7</sup>. Häufig sind die wesentlichen Funktionen eines Chipsatzes (heute noch) auf zwei Brücken–Bausteine aufgeteilt, die wegen ihrer Lage auf der senkrecht stehenden Platine anschaulich als *North Bridge* und *South Bridge* bezeichnet werden.

- Die North Bridge verbindet den Prozessor mit allen Komponenten, die einen möglichst schnellen Datentransfer benötigen. Das sind insbesondere der Hauptspeicher und die Graphikeinheit. Da die North Bridge sich insbesondere um die Steuerung der Zugriffe auf den angeschlossenen Hauptspeicher kümmern muss, wird sie auch als Speicher-Controller-Hub (Memory Controller Hub MCH) bezeichnet. Einige MCHs enthalten außerdem einen eigenen Graphikcontroller. Sie werden dementsprechend als Graphics Memory Controller Hub (GMCH) bezeichnet.

- Der zweite Baustein, die **South Bridge**, verbindet den Prozessor oder Hauptspeicher mit einer Reihe von integrierten oder extern hinzugefügten Controllern, die insbesondere zur Steuerung von Massenspeicheroder Ein-/Ausgabegeräten dienen. Daher rührt ihre Bezeichnung als Ein-/Ausgabecontroller-Hub (*I/O Controller Hub* ICH). Sie enthält dazu insbesondere eine Vielzahl von USB-2.0-Schnittstellen, über die heutzutage sehr viele externe Geräte an den PC angeschlossen werden können. Zusätzlich sichert sie die Kompatibilität zu älteren Systemkomponenten. Dazu enthält sie oft noch die vom "legendären" IBM-AT-kompatiblen

$<sup>^7\</sup>mathrm{Die}$  in der Abbildung verwendeten Bezeichnungen werden im weiteren Verlauf des Abschnitts erklärt.

Abbildung 1.6: Blockschaltbild einer Hauptplatine mit Hub-Architektur.

PC eingeführten Komponenten, wie z.B. die batteriegepufferte Echtzeituhr (Real Time Clock – RTC).

- Häufig sind einige dieser einfachen Komponenten aber auch in einem besonderen Baustein integriert, dem Super-I/O-Baustein, der über die unten beschriebene LPC-Schnittstelle an die South Bridge angeschlossen wird. Die weitere Entwicklung der PC-Technik wird die Super-I/O-Bausteine voraussichtlich überflüssig machen, da einerseits immer mehr Komponenten zusätzlich in die South Bridge integriert werden können, andererseits aber auch immer mehr Geräte über den USB an den PC angeschlossen und so einige Schnittstellen überflüssig werden. Neben den bereits erwähnten Komponenten stellt der Super-IO-Baustein oft noch alle oder einige der folgenden Schnittstellen und Komponenten zur Verfügung, auf die wir jedoch im Rahmen dieses Kurses nicht näher eingehen können:

- eine Infrarot-Schnittstelle als weit verbreitete "drahtlose" serielle

Schnittstelle (Infrared Data Association – IrDA),

- einen Tastatur- und Maus-Controller,

- einen Floppy-Disk Controller (FDC),

- einen so genannten MIDI-Port (Musical Instrument Digital Interface) zur digitalen Steuerung von Musikinstrumenten,

- einen Hardwaremonitor zur Überwachung des Rechnerzustands über Temperaturfühler und Spannungsmessern sowie zur Steuerung und Regelung der eingesetzten Lüfter,

- eine Komponente zur Steuerung und Regelung der Versorgungsspannung und der Leistungsaufnahme (*Power Management*).

- Das oben beschriebene BIOS befindet sich in einem Festwertspeicher, dem BIOS-ROM, auf der Hauptplatine, der eine Speicherkapazität von 4 bis 8 Mbit hat und im sog. *Firmware Hub* (FWH) untergebracht ist. Wegen der geringen Zugriffsgeschwindigkeiten dieser Speichertypen wird der Inhalt des BIOS-Speichers nach dem Einschalten des PCs aus dem Festwertspeicher ausgelesen und in einem besonderen Bereich des Hauptspeichers abgelegt, von dem aus er schneller bearbeitet werden kann (*Shadowing*). Üblicherweise enthält der FWH noch eine Hardwarekomponente zur Erzeugung von Pseudo-Zufallszahlen (*Random Number Generator* RNG), die z.B. für Verschlüsselungsalgorithmen benutzt werden können. Der FWH wird gewöhnlich im Multiplexbetrieb gemeinsam mit dem Super-I/O-Baustein über die unten beschriebene LPC-Schnittstelle angesprochen.

**Hub Interface**

Die beiden Brückenbausteine – North und South Bridge – sind heute durch eine schnelle dedizierte Verbindung miteinander gekoppelt, die als *Hub Interface* bezeichnet wird. Sie ist sehr viel leistungsfähiger als bei älteren Chipsätzen, bei denen die North Bridge und die South Bridge sowie alle Ein-/Ausgabeschnittstellen über den relativ langsamen PCI–Bus, der eine maximale Übertragungsrate von 133,33 MB/s erreichte, angebunden wurden. Bei Intel wird diese Verbindung als DMI (*Direct Media Interface*) bezeichnet und überträgt maximal 2 GB/s <sup>8</sup>. AMD (*Advanced Micro Devices*) setzte dafür früher den eigenentwickelten *Hypertransport*–Bus ein, der maximal bis zu 52 GB/s übertragen soll. Bei neueren Chipsätzen verwendet AMD jedoch einen 4×4 Leitungen breiten *PCI–Express–Bus* (PCIe–x4), der maximal 4 GB/s übertragen kann (s. Unterabschnitt 1.3.2.). Wie wir aus der Abbildung 1.4 sehen können, muss der MCH mit einem eigenen Kühlkörper ausgestattet werden, da er mit sehr hohe Taktraten arbeitet. Dagegen kommt der ICH meist ohne Kühlkörper aus.

Hub-Architektur

Zusammenfassend spricht man bei neueren Chipsätze meist auch von einer *Hub*-Architektur (*Hub Architecture*). Dabei ist abzusehen, dass durch die Fortschritte der Halbleiter-Integrationstechnologie konsequenterweise bereits

<sup>&</sup>lt;sup>8</sup>GB/s: Gigabyte/Sekunde, also 10<sup>9</sup> Bytes/Sekunde.

in naher Zukunft die beiden Brückenbausteine, North Bridge und South Bridge, zu einem einzigen Hub-Baustein zusammengefasst werden. So wird erwartet, dass die Firma Intel bereits Ende 2009 einen Ein-Chip-Chipsatz auf den Markt bringen wird.

#### 1.3.2 North Bridge

Wegen ihrer weit reichenden Funktionen wird die North Bridge auch als System Controller Hub bezeichnet. Sie muss den Datenfluss zwischen den verschiedenen Komponenten steuern und setzt dazu Schreib- und Leseanforderungen des Prozessors, des Graphikcontrollers oder einer Komponente an der South Bridge in Speicher-Buszyklen um. Dazu muss die North Bridge die Protokollanpassungen zwischen dem Prozessorbus, dem Speicherbus und der Graphikcontroller-Schnittestelle (s.u.) vornehmen. Zum Geschwindigkeitsausgleich speichert sie alle transportierten Daten zwischen. Dies geschieht in Registersätzen, die als Warteschlangen organisiert sind ( $First\ in.\ First\ out - FIFO$ ) und für jede Übertragungsrichtung (Read/Write – RD/WR) und Quelle/Ziel-Kombination getrennt vorhanden sind. Die Puffer besitzen unterschiedliche Größen und erlauben mit ihren dediziert ausgelegten Verbindungen den simultanen Transport von Daten.

Die Verbindung des Prozessorbausteins mit der North Bridge wird über den bereits genannten Prozessorbus vorgenommen, der auch als CPU-Bus oder – anschaulich – als Front Side Bus (FSB) bezeichnet wird. In den Anfangszei- Front Side Bus ten der Chipsätze wurde dazu der Systembus des Prozessors, bestehend aus Adress-, Daten- und Steuerbus, verwendet. Zur Erhöhung der Leistungsfähigkeit ersetzte die Firma AMD den Systembus aber schon seit Jahren durch ihre Hypertransport-Verbindung, von der gleich drei Schnittstellen auf den Prozessoren zur Verfügung gestellt werden.

HyperTransport ist eine Technologie, die für den Einsatz an verschiedensten Hypertransport Stellen einer Hauptplatine vorgesehen ist. Dabei handelt es sich um eine Punktzu-Punkt-Verbindung, die über zwei getrennte unidirektionale Pfade eine Vielzahl von Halbleiterbausteinen – also Prozessoren, Brücken, Speichereinheiten und Peripheriekomponenten – im Vollduplex–Betrieb miteinander koppelt. Die Verbindungspfade sind als parallele Busse ausgelegt. Ihre Breite kann in Abhängigkeit von den angeschlossenen Komponenten 2, 4, 8, 16 oder 32 Bit betragen, wobei die Verbindungen der beiden Ubertragungsrichtungen unterschiedliche Breiten haben können. In HyperTransport-Systemen sind Taktfrequenzen bis zu 800 MHz möglich, wobei eine Zweiflanken-Übertragung (Double Data Rate - DDR, Doubled Pumped) eingesetzt wird. Die Ubertragungsrate pro Richtung liegt damit bei 400 bis 1.600 MegaTransfers pro Sekunde (MT/s). Sie entspricht einer Datenrate von 100 bis 6.400 MB/s für jede der beiden Richtungen einer Verbindung, also einer maximalen Gesamtrate von 12,8 GB/s. Die Übertragung der Informationen geschieht in Form von kurzen Paketen mit einer maximalen Länge von 64 Bytes. Dabei werden Anforderungs-, Anwortund Rundspruchpakete unterschieden, die jeweils Befehle, Adressen und Da-

LVDS

QuickPath Interconnect

Speicher-Controller

Cache

Speicherkanal

ten enthalten können. Zur Übertragung der Signale auf den Busleitungen wird das LVDS-Verfahren (Low Voltage Differential Signalling) verwendet, das die Signale über Leitungspaare mit entgegengesetztem Signalpegel und niedrigen 1,2V-Spannungsdifferenzen schickt. (Dieses Verfahren dient zur Unterdrückung von Fehlern, die durch elektrische Störungen hervorgerufen werden. Diese Störungen wirken in der Regel auf beide Leitungen in derselben Weise ein und können daher vom Empfänger durch Differenzbildung herausgefiltert werden.) Die Firma Intel hingegen hielt sehr lange an ihrem speziellen Systembus, dem Front Side Bus (FSB) des Pentium 4, fest. Erst in der neuesten Prozessorgeneration, dem Intel Core i7, hat auch Intel den Ubergang zu einer speziellen Punkt-zu-Punkt-Schnittstelle zur North Bridge vollzogen. Der QuickPath Interconnect (QPI) besteht aus zwei einzelnen Verbindungen (Links) für jede Richtung des Datentransfers. Jeder Link überträgt 20 unidirektionale Signale in differenzieller Form, d.h. jeweils auf einem Leitungspaar in unterschiedlichen logischen Pegeln. Dazu kommt für jede Richtung noch ein Leitungspaar für die Ubermittlung eines Taktsignals, sodass der QPI insgesamt aus 84 Leitungen besteht. Von den 20 Datenleitungen werden 16 für die parallele Übertragung von Zwei-Byte-Daten benutzt, die restlichen vier werden zur Fehlerkorrektur und zur Kontrolle der Übertragungen eingesetzt. Der QPI arbeitet mit (zunächst) 3,2 GHz, wobei nach dem Zweiflankenverfahren (Double Data Rate – DDR) beide Flanken des Taktes zur Übertragung verwendet werden. Damit sollen nun Übertragungsraten bis zu 25,6 GB/s ermöglicht werden, davon je

Wesentlicher Bestandteil konventioneller North Bridges ist der Speicher-Controller (Memory Controller), der über ein oder zwei unabhängige Schnittstellen ("Kanäle") den Zugriff auf die Speichermodule des Hauptspeichers erlaubt. Uber jede Schnittstelle können Daten mit einer Ubertragungsrate von max. 12,8 GB/s geschrieben oder gelesen werden. Der Controller erzeugt – oft für unterschiedliche Typen von Speicherbausteinen – alle benötigten Steuersignale und übernimmt ggf. das Auffrischen der dynamischen Speicherbausteine (Refresh). Diese speichern die Information in winzigen Kondensatoren und würden ohne diese Maßnahme im Sekundenbereich ihre Information verlieren. Bei Verwendung eines ECC-geschützten Speichers (Error Correcting Code) übernimmt der Speicher-Controller die Überprüfung und Reaktion auf Speicherfehler durch spezielle zusätzliche ECC-Bits. Der Speicher-Controller enthält Puffer zur Bearbeitung mehrerer Schreib-/Lesezugriffe und sorgt für deren geordnete Abarbeitung. Dadurch werden insbesondere Ladezugriffe (Line Fill) auf den schnellen Zwischenspeicher, dem Cache, unterstützt. Auf den Aufbau der Speichermodule, die zur Realisierung des Hauptspeichers eingesetzt werden, gehen wir in einem eigenen Unterabschnitt 1.3.4 ausführlich ein.

12,8 GB/s für jede Übertragungsrichtung.

Bereits mit dem Athlon 64 begann die Firma AMD damit, den Speicher-Controller aus der North Bridge in den Prozessorchip selbst zu verlagern und so der CPU über dedizierte Speicherschnittstellen ("Kanäle") mit jeweils 64

Bit Breite einen schnelleren konfliktfreien Zugriff auf den Speicher zu ermöglichen. Diesen Schritt hat die Firma Intel mit ihrer Prozessorfamilie Intel Core i7 nun nachgeholt und ermöglicht den Speicherzugriff sogar über drei unabhängige Kanäle. Damit wird eine maximale Übertragungsrate von zusammen bis zu 25,6 GB/s erreicht. In Abbildung 1.6 ist die Integration des Speicher-Controllers in den Prozessorbaustein gestrichelt angedeutet.

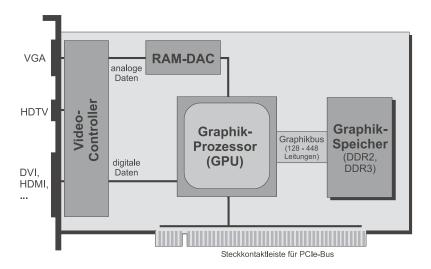

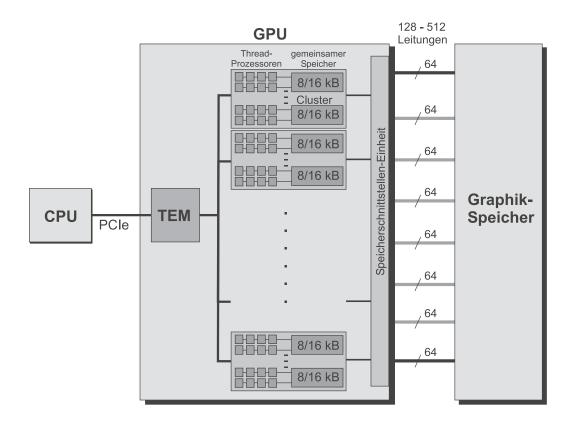

Die zweite wichtige Komponente, die über die North Bridge angesteuert wird, Graphikeinheit ist die **Graphikeinheit**, die aus einem oder zwei Graphikcontrollern besteht<sup>9</sup>. Der Anschluss der Graphikcontroller an die North Bridge geschieht heutzutage meist über den PCI-Express, auch als PCIe bezeichnet, der als skalierba- PCI-Express re Variante des älteren PCI-Busses zuerst in den Intel-Chipsätzen eingeführt wurde. Die PCIe-Verbindung wird nicht mehr als paralleler Bus ausgeführt, sondern besteht aus einer oder mehreren bidirektionalen seriellen Verbindungen, die als Lanes bezeichnet werden. Jede Lane stellt (nach der Spezifikation 2.0) eine Nutz-Transferrate<sup>10</sup> von 500 MB/s je Richtung bereit. Um auch dem Leistungsbedarf künftiger Graphikanwendungen gerecht zu werden, wurden für den Anschluss von Graphikkarten von Anfang an gleich 16 Lanes verwendet, die Ubertragungen mit 16-facher Geschwindigkeit erlauben. Die Schnittstelle, der Graphikport, wird dementsprechend mit PCIe-x16 bezeichnet und ermöglicht eine maximale Ubertragungsrate von ca. 8 GB/s in jeder Richtung, also zusammen 16 GB/s.

Bei Chipsätzen für PCs im Niedrig-Kosten-Bereich oder für den Einsatz in tragbaren Geräten (*Laptops*, *Notebooks* usw.) ist der Graphikcontroller häufig in der North Bridge selbst integriert, die dann – wie bereits gesagt – als Graphics Memory Controller Hub (GMCH) bezeichnet wird.

#### 1.3.3 South Bridge

Die Hauptaufgabe der South Bridge ist es, die Kommunikationsverbindungen und -vorgänge zwischen den unterschiedlichen Ein-/Ausgabeeinheiten zu regeln. Die Anforderungen an die Übertragungsgeschwindigkeiten dieser Verbindungen sind dabei – gemessen an den über die North Bridge laufenden Übertragungen – relativ gering. Als weitere Aufgabe stellt die South Bridge eine Reihe von internen Controllern zur Verfügung, die seit den Anfangstagen des PCs dazugehören, wie z.B. einen Zeitgeber/Zähler (Timer/Counter), eine batteriegepufferte Echtzeituhr (Real Time Clock – RTC) mit dem sog. CMOS–RAM zur Speicherung wichtiger Systemdaten sowie einen Tastatur-, DMA- (Direct Memory Access) und Interrupt-Controller (Advanced Programmable Interrupt Controller – APIC). Häufig bietet sie auch allgemein verwendbare digitale Ein-/Ausgabeleitungen (General Purpose I/O – GPIO), die der Anwender unter Programmkontrolle für beliebige Steuer- und Abfrageaufgaben einsetzen kann. Für die Kommunikation mit den Ein-/Ausgabegeräten stellt die South Bridge

<sup>&</sup>lt;sup>9</sup>Der Einsatz von zwei getrennten, aber verzahnt zusammen arbeitenden Graphikcontrollern wird insbesondere von Computerspielern geschätzt.

<sup>&</sup>lt;sup>10</sup>d.h. ohne Anrechnung von eingefügten Steuerbits

eine ganze Reihe von Standard-Ein-/Ausgabeschnittstellen zur Verfügung, die wir nun kurz behandeln wollen.

#### • Die USB-2.0-Schnittstellen

Der USB 2.0 (Universal Serial Bus) ist eine Schnittstelle zwischen Computer und Peripheriegeräten (z.B. Drucker, Scanner usw.), die von einem Firmenkonsortium definiert wurde (u.a. Compag, IBM, DEC, Intel, Microsoft) und als Ziel die einfache Erweiterbarkeit des PCs um unterschiedliche Peripheriegeräte ohne das früher übliche Kabelgewirr hatte. Der Anschluss der Geräte geschieht über eine kostengünstige Schnittstelle mit einheitlichen billigen Steckern; die Ubertragung läuft seriell über ein abgeschirmtes 4-Draht-Kabel, über das auch die Spannungsversorgung für Geräte mit niedrigem Leistungsbedarf (< 500 mA) geführt wird. An den so genannten "Wurzelknoten" (Host Controller, Root Hub) können bis zu 127 Geräte angeschlossen werden, die in Form eines Baumes angeordnet sind: Die "Blätter" werden von den Endgeräten, die Verzweigungen durch die Hubs (engl. für Nabe, Mittelpunkt, Kern...) gebildet. Das sind spezielle externe Geräte oder integrierte Einheiten mit einer Schnittstelle in Richtung des Wurzelknotens (Upstream Port) und bis zu acht Schnittstellen in Richtung der Endgeräte (Downstream Ports). Ein Hauptvorteil von USB liegt darin, dass neue Geräte bei laufendem Rechner und ohne Installation von Gerätetreibern (Hot Pluq and Play) hinzugefügt werden können. Dazu überwacht ein Hub alle an ihn angeschlossenen Geräte und ihre Versorgungsspannung. Er informiert den Host Controller über alle Änderungen, z.B. über das Entfernen oder Hinzufügen eines neuen Gerätes. Er kann jeden Downstream Port individuell aktivieren, deaktivieren oder zurücksetzen. Zwischen dem Wurzelknoten und einem Endgerät dürfen maximal sieben Kabelsegmente mit einer Gesamtlänge von 35 m, also maximal sechs *Hubs*, liegen.

Die USB–Schnittstelle überträgt Daten in drei Geschwindigkeiten, die in gemischter Form eingesetzt werden können: 1,5 Mbit/s (Low Speed), 12 Mbit/s (Full Speed) und 480 Mbit/s (High Speed), was im letzten Fall einer Rohdatenrate von maximal 60 MB/s entspricht. Die gesamte Übertragung im USB wird vom Host Controller gesteuert. Dazu fragt er in einer festgelegten Reihenfolge, aber mit unterschiedlicher Wiederholrate, alle angeschlossenen Geräte nach Übertragungswünschen ab. Dieses so genannte Polling geschieht in Zeitrahmen von 1 ms, die für die High–Speed–Übertragung noch einmal in acht 125– $\mu$ s–Rahmen unterteilt werden. Die Daten werden in Form von Datenblöcken, sog. Paketen, versendet. In jedem Rahmen gibt es reservierte Zeitschlitze für unterschiedliche Datentypen und Übertragungen:

Kontinuierlich und in Echtzeit anfallende Daten, die keine Unterbrechung und Verzögerung erlauben, werden in Form der isochro-

Root Hub

Hot Plug and Play

Low Speed, Full Speed, High Speed nen Übertragung<sup>11</sup> ausgetauscht. Es findet keinerlei Fehlerüber- isochrone wachung oder erneute Übertragung eines fehlerhaften Datenpaket Übertragung statt. Beispiele für solchermaßen übertragene Daten sind Sprach-, Audio- und Video-Daten.

- Als sog. **Interruptdaten** werden nicht periodisch, sondern spontan auftretende Datenmengen gesendet, die z.B. von der Tastatur oder der Maus stammen. Hier findet eine Fehlererkennung mit eventueller Wiederholung des Pakets statt.

- Zu den so genannten **Steuerdaten** (Control Data) zählen alle Daten zur Identifikation, Konfiguration und Überwachung der Geräte und der Hubs.

- Massendaten, d.h. größere Datenmengen ohne Echtzeitanforderungen, werden mit der Bulk-Übertragung transportiert. Hier findet eine Fehlererkennung mit eventuellen Wiederholungsversuchen statt. Typische Geräte für diese Ubertragungsart sind Drucker, Scanner und Modems.

Im USB wird der Erhalt jedes Pakets vom Empfänger quittiert. Dazu hat der drei Möglichkeiten: Er kann den fehlerfreien Erhalt durch ein ACK-Quittungspaket bestätigen (Acknowledge) bzw. den fehlerhaften Fall durch das Auslassen dieser Quittung anzeigen. Durch ein NAK-Paket Quittungspaket (Non Acknowledge) kann er mitteilen, dass momentan kein Senden oder Empfangen eines Pakets möglich ist. Durch ein STALL-Paket wird angezeigt, dass das angesprochene Gerät außer Betrieb oder ein Eingriff des Host Controllers nötig ist.

#### • Die FireWire-Schnittstelle (IEEE 1394)

Der IEEE-1394-Bus ist eine standardisierte Weiterentwicklung der Fire-Wire-Schnittstelle der Firma Apple<sup>12</sup>. Typische Anwendungen liegen in den Bereichen Audio, Video und Multimedia, wo man ihn z.B. in Festplatten, CD-ROM- und DVD-Laufwerken und -Brennern findet. So wird er insbesondere als i.Link in CamCordern häufig eingesetzt. Der Standard i.Link-IEEE 1394a sieht Übertragungsraten bis zu 400 Mbit/s vor, der Standard Schnittstelle IEEE1394b solche bis 3200 Mbit/s. Dabei unterstützt er – wie der USB – neben der asynchronen auch die isochrone Übertragung. Bei der asynchronen Übertragung wird wiederum jedes Paket vom Empfänger durch ein Quittungspaket (ACK) beantwortet und im Fehlerfall automatisch wiederholt. Bei der isochronen Übertragung wird auf diese Quittierung verzichtet. Andere Gemeinsamkeiten mit dem USB sind die kostengünstigen Stecker und Verbindungskabel, die einfache Erweiterbarkeit des Bussystems, die (eingeschränkte) Spannungsversorgung über das Anschluss-

<sup>&</sup>lt;sup>11</sup>Isochron bedeutet sinngemäß: zum gleichen Zeitpunkt im Zeitrahmen auftretend.

<sup>&</sup>lt;sup>12</sup>Vereinfachend bezeichnen wir im Weiteren den Bus meist nur noch als FireWire.

kabel, das Hinzufügen bzw. Entfernen von Geräten während des Betriebs (*Hot Plug and Play*).

Anders als eine USB-Vernetzung hat ein System, das auf dem FireWire basiert, keine Baumstruktur. Hingegen lässt der FireWire fast beliebige Netzstrukturen zu – solange dabei keine Schleifen auftreten. Alle Verbindungen sind Punkt-zu-Punkt-Verbindungen, wobei in den Endgeräten Verzweigungen realisiert werden können. Dabei kann jeder Knoten im FireWire bis zu 27 Anschlüsse (*Ports*) für weitere Knoten besitzen. Zur Kopplung von FireWire-Bussen können aber auch externe Einheiten, sog. Repeater oder Brücken (Bridges), eingesetzt werden. Insgesamt kann ein FireWire-System maximal 1023 Teilbusse mit jeweils höchstens 63 Knoten umfassen. Auf den Verbindungsleitungen können unterschiedliche Ubertragungsgeschwindigkeiten verwendet werden. Die Knoten im Fire-Wire sind Rechner oder Endgeräte, wobei Busse aber auch ohne Rechner arbeiten können. Das heißt, dass – anders als beim USB – eine Datenübertragung auch direkt zwischen Endgeräten stattfinden kann. Das Bussystem ist selbstkonfigurierend, d.h. nach dem Einschalten oder Rücksetzen ermitteln die Knoten selbst, wer von ihnen die Funktion des Wurzelknotens (Root Node) wahrnehmen darf. Die maximale Entfernung zwischen zwei Knoten beträgt beim FireWire mit Kupferkabel-Verbindungen ungefähr 72 m, durch Einsatz einer Glasfaserverbindung können bis zu 1600 m überbrückt werden. Dabei dürfen zwischen zwei Knoten höchstens 16 Kabelsegmente liegen.

#### • Die PCI-Bus-Schnittstelle

Der PCI–Bus (Peripheral Component Interconnect) war lange Zeit der am weitesten verbreitete Busstandard für Ein–/Ausgabekarten. Er wurde ursprünglich von Intel eingeführt. Später fand man aber PCI–Steckplätze bei allen Desktop–Computern, d.h. PCI wurde auch durch Chipsätze anderer Prozessorhersteller unterstützt. Der PCI–Bus überträgt die Daten entweder auf einem 32–Bit–Datenbus mit (gerundet) 33,33 MHz oder einem 64–Bit–Datenbus, der mit (gerundet) 66,67 oder 133,33 MHz (extended PCI bzw. PCI–X) getaktet wird. Dabei ist der PCI–X kein Bus im herkömmlichen Sinne mehr, sondern eine Punkt–zu–Punkt–Verbindung zum Anschluss einer einzigen Komponente. Aus den Kenndaten ergibt sich eine Datentransferrate von 533,33 MB/s bis zu 1,067 GB/s. <sup>13</sup> Der PCI–Bus wird auf modernen Hauptplatinen nur noch aus Kompatibilitätsgründen als "Erblast" (Legacy) implementiert und wird wohl über kurz oder lang vom Markt verschwinden. Deshalb wollen wir ihn im Rahmen dieses Kurses nicht weiter beschreiben.

#### • Die PCIe-Schnittstellen

Das Grundkonzept des PCIe (auch: PCI–E) wurde bereits im Unterabschnitt 1.3.2 kurz beschrieben. Der PCIe wurde ab 2004 von der Firma

<sup>&</sup>lt;sup>13</sup>Genauere Werte bekommt man, wenn man – anstatt mit den gerundeten Datentransferraten – mit den entsprechenden Schwingungsdauern 30, 15 bzw. 7,5 ns rechnet.

Intel eingeführt; inzwischen werden seine Spezifikationen von einer Firmengruppe (PCI Special Interest Group – PCI-SIG) betreut, der fast alle namhaften Chiphersteller angehören. Beim PCIe handelt es sich um eine skalierbare, d.h. den Anforderungen des Einsatzbereichs anpassbare Anzahl von seriellen Punkt-zu-Punkt-Verbindungen, den sog. Lanes (Bahn, Weg), die die angeschlossenen Bausteine über schnelle Schaltein- Lane heiten mit dem Computersystem verbinden. Durch die Bündelung von mehreren parallelen PCIe-Lanes können leicht verschiedene, den jeweiligen Erfordernissen angepasste Übertragungsbandbreiten realisiert werden. Die Anzahl der Lanes einer Verbindung wird mit einem kleinem vorangestellten x angegeben. So sind also Systeme mit PCIe-x1, PCIex2 bis zu PCIe-x32 möglich. (Im PC-Bereich sind bis heute jedoch nur Systeme bis zu PCIe-x16 realisiert.) Durch die Anpassung der Anzahl der Lanes an die Erfordernisse einer Verbindung spart man u.U. sehr viele Verbindungsleitungen, denn insgesamt werden für eine Lane nur vier Leitungen benötigt, je zwei für eine Richtung. 14 Durch diesen drastischen Wegfall von Leitungen vereinfachen und verbilligen sich auch die Steckverbindungen. Die sind so realisiert, dass eine Erweiterungskarte mit nLanes auch in einen Slot für m Lanes eingesetzt werden kann, solange m > n ist.

Anders als beim Vorgänger, dem PCI-Bus, der die vom Prozessor ausgegebenen Adressen und Daten direkt übertrug, werden im PCIe die Daten in Form von Paketen übertragen. Das sind Datenblöcke, die durch einen Pakete Paketkopf mit Quelladressen und Paketnummer sowie eine Prüfsumme am Ende (Cyclic Redundancy Check – CRC) ergänzt werden. Werden durch die Prüfsumme Übertragungsfehler angezeigt, so fordert der PCIe-Controller automatisch eine erneute Aussendung desselben Pakets an. Durch die Paketnummer wird sichergestellt, dass das erneut ausgesendete Paket vom Empfänger in die richtige Reihenfolge gesetzt werden kann, auch wenn bereits Folgepakete eingetroffen sind.

Im Gegensatz zum älteren PCI-Bus gibt es bei PCI-Express keine Einsteckplätze (Slots) an einem gemeinsamen Bus, sondern geschaltete Ports. Dies bedeutet, dass den einzelnen PCI-Express-Karten stets die volle Bandbreite zur Verfügung steht, da hier keine Zugriffskonflikte wie beim PCI-Bus auftreten können. Die South Bridge ist dabei in der Lage, simultan über mehrere PCIe-Verbindungen Daten und das in beiden Richtungen – vom bzw. zum Gerät – zu übertragen. Dazu verwendet sie einen sog. Kreuzschienenschalter (Crossbar Switch), der es erlaubt, der mehre- Kreuzschienenschalter re Quellen von Datenübertragungen mit ihren jeweilige Zielen gleichzeitig verbinden kann.

<sup>&</sup>lt;sup>14</sup>Auf jedem Leitungspaar werden die Signale zur Erhöhung der Störsicherheit differentiell übertragen, d.h. mit jeweils entgegengesetztem logischen Pegel. Störungen wirken sich in der Regel auf beide Leitungen gleichartig aus und können daher durch die Differenzbildung der Pegel herausgefiltert werden.

PCIe-x32

ATA

IDE-Kanal

**ATAPI**

Master, Slave

Die PCIe-Spezifikation sieht auch vor, dass Einsteckkarten im laufenden Betrieb gewechselt werden können (*Hot Plugging*). Von dieser Fähigkeit könnten vor allem mobile Systeme wie Notebooks profitieren. Neben der im Unterabschnitt 1.3.2 erwähnten Verbindung von Graphikadapter mittels PCIe-x16 sind im Serverbereich durch den Maximalausbau von 32 *Lanes*, PCIe-x32 genannt, auch bidirektionale Hochgeschwindigkeitsverbindungen mit bis zu 16 GB/s pro Übertragungsrichtung, also insgesamt 32 GB/s möglich.

#### • Die IDE-Schnittstellen

Die IDE-Schnittstelle ist technisch überholt und wird für neue Festplatten nicht mehr verwendet. Da sie aber auch auf modernen Hauptplatinen noch vorhanden ist (vgl. Abbildung 1.4), soll sie hier kurz beschrieben werden.

IDE (*Integrated Drive Electronics*) ist eine standardisierte Schnittstelle zum Anschluss von nichtflüchtigen Speichermedien, wie Festplattenlaufwerken, CD-ROMs und DVD-Laufwerken. Sie ist auch unter dem Namen ATA (*Advanced Technology Attachment*) bekannt. Die Beschränkung auf Plattengrößen von 528 MB wurde durch die Erweiterung zu EIDE (Extended IDE) aufgehoben. Die maximale Datenrate des EIDE-Busses 133 MB/s. Man muss allerdings beachten, dass diese Datenrate nur dann erreicht wird, wenn die Laufwerkselektronik die Daten bereits in ihrem internen (Cache-) Speicher hat. Die permanente Datenrate zwischen Festplatte und Laufwerkselektronik liegt deutlich unter dem o.g. Wert.

Das IDE Interface bietet zwei getrennte Schnittstellen ("Kanäle") für den Anschluss von Massenspeichergeräten, also Festplatten– (Hard Disk Drive – HDD), CD–ROM–, DVD–Laufwerken (Digital Versatile Disk) und natürlich die immer beliebter werdenden Programmiergeräte für CD–ROMs oder DVDs ("Brenner"). Die Bezeichnung IDE (Integrated Drive Electronics) zeigt an, dass diese Schnittstelle Geräte mit integrierten Controllern verlangt und selbst keinerlei Ansteuerlogik zur Verfügung stellt. Die IDE–Schnittstellen im PC wurden von der ANSI (American National Standards Institute) standardisiert. Diese "genormten" Schnittstellen wurden zuerst im IBM–AT–PC eingesetzt und tragen daher die Bezeichnung ATA (Advanced Technology Attachment). Die anschließbaren Geräte werden dementsprechend ATAPI–Geräte (ATA Packet Interface) genannt.

Die beiden o.g. Kanäle werden als primärer und sekundärer Kanal (*Primary, Secondary Channel*) bezeichnet und erlauben jeweils den Anschluss von bis zu zwei Geräten. Diese werden *Master* und *Slave* genannt. Sie müssen ihre Funktion durch kleine Steckbrücken auf ihrer Platine und ihre Platzierung in den entsprechenden Steckplatz zugewiesen bekommen. Jedes der maximal 4 IDE–Geräte kann unabhängig voneinander durch die IDE–Schnittstelle aktiviert oder deaktiviert werden. Die Deaktivie-

rung versetzt die Leitungen des "abgeschalteten" Gerätes in den (hochohmigen) Tristate-Modus. In diesem Modus kann das Gerät während des Betriebs des PCs aus dem Rechner entfernt bzw. (wieder) eingesetzt werden ( $Hot\ Swap$ ).

Die ANSI hat im Laufe der Jahre eine ganze Reihe von Standards der ATA-Schnittstelle erstellt, die sich insbesondere durch die Übertragungsleistung der Schnittstelle unterscheiden. Üblich sind heute die Standards Ultra-ATA/66 und Ultra-ATA/100, die (theoretisch) eine maximale Uber- Ultra-ATA tragungsrate von 66 bzw. 100 MB/s erreichen. Diese Raten werden jedoch nur im DMA-Modus erreicht, bei dem der Gerätecontroller als Bus Master selbst die Datenübertragung durchführt. (Daher stammt auch die häufig verwendete Bezeichnung: UltraDMA – UDMA.) Außerdem werden sie nur bei Lesezugriffen erreicht. Schreibzugriffe ermöglichen nur eine um ca. 10 % geringere Ubertragungsrate (88,9 MB/s). Noch langsamer sind die sog. PIO-Zugriffe (*Programmed Input/Output*), bei denen der Prozes- PIO-Modus sor jedes Datum selbst übertragen muss. Hier werden maximal 16 MB/s erreicht.

Die IDE-Schnittstellen können in zwei verschiedenen Modi arbeiten:

- Im sog. Legacy Mode müssen den Geräten der IDE-Kanäle bestimm- Legacy Mode te Eingänge des Interrupt-Controllers fest zugewiesen werden. Wie weiter unten beschrieben, sind dies IRQ14 und IRQ15. Außerdem werden die Steuer- und Statusregister ihrer Controller und festgelegten Adressen im Ein-/Ausgabe-Adressbereich (I/O Address Space) des Prozessors angesprochen.

- Im Native Mode werden sie über spezielle Register in ihrem Kon- Native Mode figurationsbereich definiert und benötigen daher keine festgelegten Interrupt-Eingänge und I/O-Adressen.

#### • Die serielle ATA-Schnittstelle (SATA, eSATA)

Das Serial ATA Interface (SATA Interface) wurde aus dem oben beschriebenen IDE/ATA-Standard entwickelt und dient wie dieser dem Datenaustausch mit nichtflüchtigen Speichermedien. Um die Zahl der benötigten Adern zu verringern und damit die Kabelführung zu vereinfachen, wurde ein serielles Übertragungsprotokoll eingeführt. Kompatibilität wird durch SATA/ATA-Adapter erreicht, über die SATA-Geräte auch an der IDE-Schnittstelle eingesetzt werden können (Standard-ATA Emulation).

Während die erste SATA-Spezifikation eine Datenrate von 150 MB/s vorsah, arbeitet der neue Standard SATA Revision 2.x (bzw. SATA 3Gb/s+) bereits mit der doppelten Datenrate von 300 MB/s, was einer Brutto-Datenrate von ca. 3 Gbit/s entspricht. Daraus resultiert die gebräuchliche LVDS

Bezeichnung SATA/300.<sup>15</sup> Um diese hohen Datenraten sicher zu erreichen, benutzt man die Signalübertragung mit dem so genannten LVDS-Verfahren (*Low Voltage Differential Signalling*), das zur Unterdrückung von Fehlern, die durch elektrische Störungen hervorgerufen werden, die Signale über Leitungspaare mit entgegengesetztem Signalpegel und niedrigen Spannungsdifferenzen überträgt.

Das SATA Interface stellt ebenfalls zwei unabhängig arbeitende Schnittstellen (gekennzeichnet durch 0 bzw. 1 in den Signalbezeichnungen), die jede für sich aktiviert und deaktiviert werden kann. Diese Schnittstellen werden durch zwei unabhängige Controller im Bus Master—Modus betrieben, d.h. sie können selbständig auf den Hauptspeicher zugreifen. Im Unterschied zum Standard—ATA sind jedoch nur Punkt—zu—Punkt—Verbindungen, also keine Master/Slave—Konfigurationen möglich. Insgesamt können somit nur bis zu zwei SATA—Geräte, d.h. Festplattenlaufwerke (Hard—Disk Drive — HDD) oder ATAPI—Geräte, betrieben werden. Im Gegensatz zur parallelen ATA—Schnittstelle ist mit SATA ein Wechsel des Speichermediums im laufenden Betrieb möglich (Hot Plugging). Jedoch ist ein unerwartetes Entfernen bzw. Hinzufügen eines SATA—Gerätes nicht zulässig; es muss erst durch Software vorbereitet werden, indem z.B. das Betriebssystem die gewünschte Schnittstelle in den Power—Down—Modus schaltet.

Der SATA-Standard sieht nur den Anschluss von Geräten innerhalb des PCs vor. Die eingesetzten Kabel sind deshalb nicht gegen elektromagnetische Störungen abgeschirmt und die Stecker nicht für den Anschluss von externen Geräten ausgelegt. Um auch den externen Anschluss von Geräten über die SATA-Schnittstelle zu ermöglichen, wurden im neuen Standard auch Vorgaben zu externen Steckern und Anschlusskabeln gemacht. Diese Vorgaben definieren nun die externe serielle ATA-Schnittstelle – External Serial ATA oder kurz eSATA.

#### • Die Audio-Schnittstelle

Heutzutage finden sich auf den PC-Hauptplatinen Audio-Schnittstellen, die zwei verschiedenen Standards genügen.

Der ältere Standard ist die AC'97-Schnittstelle (AC'97 Link).

Sie bietet dem PC-Entwickler die Möglichkeit, sehr kostengünstig Audio- und Modemfunktionen schon auf der Hauptplatine (Onboard Sound) zu realisieren und auf den Einsatz einer teuren Audio-Steckkarte (Soundcard) zu verzichten. Für diese Funktionen ist lediglich ein so genannter Codec (Codierer/Decodierer, besser: Converter/Deconverter) erforderlich, der in einem einzigen Baustein einen Analog/Digital- sowie einen Digital/Analog-Wandler für mehrere

eSATA

AC'97-Schnittstelle

<sup>&</sup>lt;sup>15</sup>Wird jedoch eine SATA–Schnittstelle im PIO–Modus betrieben, so reduziert sich die Übertragungsrate auf maximal 16 Mbit/s.

(Stereo-)Kanäle zur Verfügung stellt. Bei dieser einfachen Lösung muss jedoch der Prozessor die "Rechenaufgaben" zur Erzeugung von Audio-/Modem-Signalen übernehmen, die auf einer "Soundkarte" von Spezialchips geleistet werden. Maximal sechs verschiedene Codecs können über die AC'97-Schnittstelle mit Ausgabedaten versorgt werden. Diese werden ihnen im Zeit-Multiplexverfahren (Time Division Multiplex Access – TDMA) über eine einzige Leitung zugeführt. Man spricht in diesem Fall von bis zu sechs "Ausgabekanälen". Bei den Codecs kann es sich um Audio-Codecs (AC), um Modem-Codecs (MC) oder aber um kombinierte Audio/Modem-Codecs (AMC) handeln. Die AC'97-Schnittstelle verfügt häufig über einen gesonderten Steckplatz, der mit AMR (Audio/Modem Riser Slot) bezeichnet wird und z.B. eine Steckkarte zum Anschluss des PCs an das Telefonnetz aufnehmen kann.

– Die Audio-Schnittstelle moderner Hauptplatinen genügt den Anforderungen des *High Definition Audio*—Standards (HD-Audio), HD-Audio der im Jahr 2004 erlassen wurde und auf Entwicklungen der Firma Intel beruht. Längerfristig soll der HD-Audio-Standard die oben beschriebene AC'97-Schnittstelle ablösen. Audio-Controller nach dem HD-Audio-Standard übertragen Stereo-Signale mit einer Abtastrate von 192 kHz und einer Datenbreite von 32 Bits in bis zu acht getrennten Zeitkanälen (im sog. Zeitmultiplex-Verfahren, Time Di-Zeitmultiplexvision Multiplex Access – TDMA). Gibt man diese Kanäle auf sie- Verfahren ben Lautsprechern und einem speziellen Bass-Lautsprecher (Subwoofer) aus, so erhält man z.B. eine Rundum-Beschallung, die als 7.1 Surround bezeichnet wird. Der Standard sieht aber auch die simultane Ausgabe von zwei oder mehr unabhängigen Audio-Strömen vor. So kann man sich z.B. mit fünf Lautsprechern und dem Bass-Lautsprecher (5.1 Surround) für den Musikgenuss zufrieden geben und die beiden restlichen Kanäle z.B. für eine zweite (Sprach-)Übertragung über einen Kopfhörer benutzen. Auch andere Aufteilungen sind möglich, um so z.B. zwei verschiedene Ausgaben in zwei verschiedenen Räumen zu unterstützen.

Der Standard erweitert auch die Möglichkeiten zur gleichzeitigen Aufzeichnung von Tönen, Geräuschen, Sprache und Musik durch eine Vielzahl von unabhängigen Mikrophonen (Array Microphone). Dadurch wird insbesondere die Spracherkennung und die "verständliche" Übermittlung von Sprache über das Internet (Voice over IP) unterstützt.

#### • Die Netzwerkschnittstelle (LAN-Link)

PCs sind in der Regel an ein Lokales Netz (Local Area Network – LAN) Lokales Netz angeschlossen. Dabei handelt es sich meist um das so genannte Ethernet, bei dem alle Rechner auf dasselbe physische Verbindungsmedium Ethernet

MAC-Schicht

PHY-Schicht

MAC-Controller PHY-Controller zugreifen und daher Kollisionen auftreten können. Zur Strukturierung der verwendeten Hard- und Software-Technologien und Protokolle wird die Netzwerkschnittstelle eines Rechners gewöhnlich in mehrere Schichten eingeteilt ("Schichtenmodell"). Die beiden unteren Schichten des Schichtenmodells sind die MAC-Schicht (*Media Access Control Layer*) und die PHY-Schicht (*Physical Layer*). Die MAC-Schicht regelt hauptsächlich den kollisionsfreien Zugriff auf das gemeinsam genutzte Medium. Die unterste PHY-Schicht beschäftigt sich mit den mechanischen und physikalischen Eigenschaften des Verbindungsmediums und um die bitweise Datenübertragung über diese Verbindung.<sup>16</sup>

Die Netzwerkschnittstellen-Hardware eines PCs besteht in der Regel aus zwei Controllern, die die erwähnten beiden unteren Schichten des Ethernet realisieren, also einem MAC- und einem PHY-Controller. Je nach Aufbau des Chipsatzes existieren heute drei Lösungsansätze:

- Beide Controller sind extern in getrennten Bausteinen realisiert. Die Ankopplung des MAC-Controllers an die South Bridge geschieht z.B. über den oben beschriebenen PCIe. Die Verbindung zwischen den Controllern geschieht über eine dedizierte schnelle Schnittstelle, die z.T. mehrfach für unterschiedliche Übertragungsgeschwindigkeiten vorhanden sein muss.

- Beide Controller sind zusammen in einem externen Ethernet-Controller, also außerhalb der South Bridge, realisiert. Auch in diesem Fall bietet die South Bridge eine spezielle schnelle Schnittstelle zum Ethernet-Controller oder verwendet dazu den PCIe.

- Der MAC-Controller ist in der South Bridge integriert, der PHY-Controller muss extern als eigenständiger Baustein ergänzt werden. In diesem Fall werden beide Bausteine durch die im ersten Fall beschriebenen dedizierten Schnittstellen verbunden, die nun von der South Bridge zur Verfügung gestellt werden.

Moderne PCs unterstützen verschiedene Ethernet-Standards, die den Netzwerkanschluss über verdrillte Paare von Kupferkabeln (*Twisted Pair*) vornehmen: Das Standard-Ethernet überträgt mit 10 Mbit/s, das Fast-Ethernet mit 100 Mbit/s und das Gigabit-Ethernet mit 1000 Mbit/s (1 Gbit/s). Ethernet überträgt die Daten in Form von Paketen, die – neben einer jeweils 6 Byte langen Empfänger- und Sender-Adresse und einer 4 Byte langen Prüfsumme – bis zu 1500 Byte von Benutzerdaten enthalten können.

• Der SMBus Der SMBus (*System Management Bus*) verbindet wichtige Komponenten der Hauptplatine miteinander. Eine seiner Aufgaben ist

Ethernet-Standards

<sup>&</sup>lt;sup>16</sup>Sie wird daher im Deutschen als Bitübertragungsschicht bezeichnet.

es, Steuer- und Überwachungsinformationen zwischen den Brückenbausteinen und den Speichermodulen zu übertragen. Er unterstützt außerdem Uberwachungsfunktionen (Monitoring) der folgenden Bauteile und physikalischen Größen: Batterie, Lüfter, Temperaturen, Betriebsspannungen für alle Komponenten, PCI-Takt, unterschiedliche Betriebszustände (Power-Down-Modi, Prozessor-Stop-Modus) usw. Die Ergebnisse seiner Uberwachungsfunktion kann er durch Meldung an den Prozessor weiterreichen. Der SMBus erlaubt häufig auch einem externem Mikrocontroller den Zugriff auf bestimmte Systemkomponenten.

Der SMBus ist ein langsamer serieller Bus, der aus dem von der Firma Philips vor ca. 20 Jahren entwickelten I<sup>2</sup>C-Bus zur Verbindung von I<sup>2</sup>C-Bus Integrierten Bausteinen (ICs) hervorging. Er besitzt ein einfaches Ubertragungsprotokoll.

#### • Die LPC-Schnittstelle

Die wichtigsten Peripheriekomponenten, wie Tastatur- und Maus-Controller usw. sind häufig in einem externen Baustein, dem Super-I/O-Baustein (vgl. Abbildung 1.6), untergebracht, der an der South Bridge über die LPC-Schnittstelle (Low Pin Count) mit insgesamt neun Signalen angeschlossen ist. Adressen und Daten werden über vier Leitungen nacheinander und in mehreren Teilen übertragen (Multiplexbetrieb). Von den restlichen Signalen dient jeweils eines zur Ubermittlung des Taktes bzw. zur Kennzeichnung einer laufenden Übertragung. An der LPC-Schnittstelle ist sehr oft auch das BIOS-ROM im Firmware Hub (FWH) angeschlossen.

#### • Der Interrupt-Controller

In einem komplexen Mikrorechner-System wie einem PC werden immer wieder Unterbrechungsanforderungen durch die Peripheriekomponenten an den Prozessor gestellt. Diese so genannten Interrupts werden dem Interrupt Prozessor in regelmäßigen oder unregelmäßigen zeitlichen Abständen über spezielle Leitungen übermittelt. Sie zeigen dem Prozessor z.B. an, dass eine Komponente Daten übertragen will oder die Ausführung einer Routine zur Durchführung einer bestimmten Aktion wünscht. Da dazu nicht jeder Komponente eine eigene Leitung zur Verfügung gestellt werden kann, muss ein Interrupt-Controller eingesetzt werden, der insbesondere auch die Aufgabe hat, gleichzeitig vorliegende Unterbrechungsanforderungen in eine geeignete Prioritäten-Reihenfolge zu setzen und dem Prozessor über Prioritäten die Anforderungsquelle mit momentan höchster Priorität zu informieren.

Der in der South Bridge integrierte Interrupt-Controller unterstützt drei unterschiedliche Möglichkeiten, Unterbrechungsanforderungen der Peripheriekomponenten anzunehmen und zum Prozessor weiterzuleiten.

- In der ersten Version, die als "Altlast" (Legacy) vom IBM AT-PC der 80er Jahre des letzten Jahrhunderts übernommen wurde, besitzt der IRQ-Router

IDE-Kanäle

serielle Interrupt-Anforderung

APIC

Interrupt–Controller 15 Eingänge (IRQ0,...,IRQ15 – ohne IRQ2)<sup>17</sup>, die den verschiedenen Interrupt–Quellen zugeordnet werden. Dazu enthält die South Bridge eine besondere Schaltung, IRQ–Router genannt, die die Unterbrechungssignale der internen Brückenkomponenten mit den oben erwähnten Eingängen IRQ0,...,IRQ13 (ohne IRQ2) des Interrupt–Controllers verbindet. Die Eingänge IRQ14 und IRQ15 werden über zwei Anschlüsse der South Bridge nach Außen geführt. Sie sind für die Geräte reserviert, die an den IDE–Schnittstellen betrieben werden, und zwar IRQ14 für den primären Kanal (Primary Channel, s.u.) und IRQ15 für den sekundären Kanal (Secondary Channel). Akzeptierte Unterbrechungsanforderungen reicht der Interrupt–Controller über ein Ausgangssignal (INTR) an den Prozessor weiter.

Bei der zweiten Variante werden Unterbrechungsanforderungen seriell über eine einzelne (bidirektionale) Leitung (Serial Interrupt Request – SERIRQ) an den Interrupt-Controller weitergereicht. Dazu werden über SERIRQ Zeitrahmen aus 32 Schlitzen (Slots), eingerahmt durch einen Start- und einen Stop-Slot, ausgesandt. Jeder Slot kann einer möglichen Interrupt-Quelle zugewiesen werden. Einige Slots sind für spezielle Anforderungen reserviert, darunter die oben genannten 15 Unterbrechungssignale IRQ0,...,IRQ15 (ohne IRQ2). Die restlichen Slots sind frei belegbar.

Jede Komponente, die eine Unterbrechungsanforderung an den Interrupt-Controller stellen will, markiert dies in dem ihr zugewiesenen Slot des SERIRQ-Zeitrahmens. Der Interrupt-Controller wertet den empfangenen Zeitrahmen aus, entscheidet über die Unterbrechungsanforderung mit der momentan höchsten Priorität und leitet sie über das o.g. Signal INTR an den Prozessor weiter.

In der dritten Variante benutzt der Brückenbaustein eine Erweiterung des oben beschriebenen Interrupt-Controllers, die als APIC (Advanced Programmable Interrupt Controller) bezeichnet wird. Dieser Controller unterstützt bis zu 24 verschiedene Interrupt-Quellen, die seinen Eingängen IRQ0,...,IQR23 zugewiesen werden. Dabei werden die IDE-Geräte – wie oben beschrieben – wiederum mit den externen Eingängen IRQ14 und IRQ15 verbunden. Die IRQ-Eingänge IRQ16,...,IRQ23 werden insbesondere von den internen Komponenten (USB, LAN Link usw.) benutzt.

Der APIC unterscheidet sich von der oben beschriebenen "Legacy"-Variante insbesondere durch die Art, wie die Unterbrechungsanforderungen der Komponenten an den Controller herangeführt werden. Dies geschieht nicht durch die Eingangssignale des Interrupt-

<sup>&</sup>lt;sup>17</sup> Die Abkürzung IRQ steht für *Interrupt Request*.

Controllers, sondern durch "normale" Schreibzugriffe auf den Hauptspeicher. Dazu wird dem APIC eine bestimmte Speicherzelle zugewiesen, die als *IRQ PIN Assertion Register* (IRQPA) bezeichnet wird. In dieses "Register" schreibt eine "unterbrechungswillige" Komponente ihre spezifische Kennung, die so genannte Interrupt–Vektornummer (IVN).

Der APIC liest die IVN aus dem IRQPA-Register, aktiviert den entsprechenden Interrupt-Eingang und löscht sofort das IRQPA-Register für die nächste Anforderung. Er entscheidet dann über die Prioritäten der aktuellen Unterbrechungsanforderungen. Dabei wird die Prioritäten-Reihenfolge nicht durch die Nummern der zugeordneten Controller-Eingänge festgelegt, sondern sie kann frei zugeordnet werden. Die Interrupt-Vektornummer wird einer Komponente bei der Systeminitialisierung zugewiesen und in ein bestimmtes Register ihres Konfigurationsbereichs eingetragen.

Neben der oben beschriebenen "konventionellen" Methode, die Unterbrechungsanforderung über das Signal INTR an den Prozessor weiterzureichen, kann der APIC ein weiteres Verfahren dazu anwenden – sofern dieses vom Prozessor unterstützt wird. Dieses wird als FSB Interrupt Delivery bezeichnet. Hierbei schreibt die South Bridge eine "Unterbrechungsnachricht" (Interrupt Message) in bestimmte Speicherzellen des Hauptspeichers. Durch diese Nachricht und ihre Zieladresse wird die Interrupt—Quelle spezifiziert – für den Einsatz in einem Mehrprozessorsystem aber auch der angesprochene Prozessor.

Der Prozessor liest regelmäßig die Speicherzellen und informiert sich dadurch über eventuelle Unterbrechungswünsche. Aus der gefundenen IVN ermittelt er die Startadresse der verlangten Unterbrechungsroutine (*Interrupt Service Routine* – ISR) und führt sie aus.

Die Vorteile des beschriebenen APIC-Verfahrens sind:

- \* Die Durchführung eines speziellen Buszugriffes zur Ermittlung der IVN (*Interrupt Acknowledge Cycle*) ist nicht nötig.

- \* Es wird keine zusätzliche Busleitung zum Prozessor verlangt.

- \* In einem System sind mehrere APICs mit eigenen Interrupt-Vektoren einsetzbar – insbesondere in einem Mehrprozessorsystem.

- Die Prozessor- und Systemsteuerung Die Prozessor- und Systemsteuerung übernimmt üblicherweise die Funktion der Steuerung und Regulierung des Energieverbrauchs im PC. Diese Komponente wird Advanced Configuration and Power Interface (ACPI) genannt. Durch ACPI ACPI kann das Betriebssystem nach Vorgaben im BIOS vielfältige Aufgaben übernehmen, die werbewirksam als TCO-Funktionen (Total Cost of Ownership) bezeichnet werden, da sie helfen sollen, die Gesamtkosten für TCO den PC-Besitzer zu vermindern:

- Steuerung und Überwachung der Systemkomponenten,

- Steuerung der Leistungsaufnahme (Power Management ACPI/APM) durch verschiedene Stromspar-Systemzustände (Low-power States) und der Deaktivierung nicht gebrauchter Komponenten und Schnittstellen (AC'97 bzw. HDA für Audio und Modem, ATA/IDE, SATA, LAN, USB, SMBus),

- Takterzeugung und -überwachung,

- Systemdiagnose und Meldung von Fehlern; dazu gehören z.B. ECC-Fehler, aber auch Warnungen, wenn das PC-Gehäuse geöffnet wird (Intruder Detect),

- Behebung von Systemblockaden, zu deren Erkennung die Zeitgeber-Bausteine (*Timer*) verwendet werden.

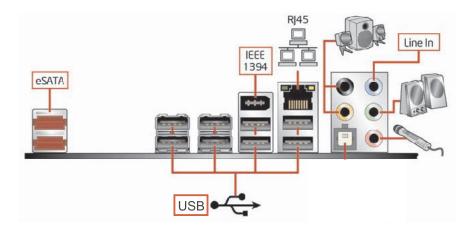

Steckermodul

Bei heutigen Hauptplatinen werden die unterschiedlichen Komponenten der South Bridge in einem besonderen Platinenbereich mit einem Steckermodul verbunden, das durch eine Aussparung im Gehäuse nach Außen zugängig ist. Die Lage dieses Steckermoduls wurde bereits in Abbildung 1.4 gezeigt. Abbildung 1.7 zeigt für die dort dargestellte Hauptplatine Intel DX48BT2 die "Außenansicht" des Steckermoduls mit den verschiedenen Anschlüssen der beschriebenen Schnittstellen.

Abbildung 1.7: Ein Schnittstellenmodul.

Das gezeigte Steckermodul bietet acht USB-Anschlüsse. Die zugehörige Hauptplatine bietet, wie fast alle modernen Hauptplatinen, darüber hinaus noch weitere, leichter zugängliche USB-Anschlüsse auf der Frontplatte oder einer Seite des PC-Gehäuses. Die Kennung RJ45 in der Abbildung steht für den Anschluss der Netzwerkschnittstelle, zusätzlich gekennzeichnet durch die Skizze eines kleinen Rechnernetzes. Lautsprecher, Mikrophon und *Line In*<sup>18</sup> kennzeichnen die

$<sup>^{18}</sup> Line\ In$  bezeichnet die Steckbuchse für ein Audio–Eingabegerät, das – anders als das Mikrophon – ohne Vorverstärker auskommt, also z.B. der Ausgang einer Stereoanlage.

Anschlüsse der Audio–Schnittstelle. Auch diese ist häufig zusätzlich im vorderen Bereich des PC–Gehäuses zugängig.

#### 1.3.4 Hauptspeicher

**SDRAM**

Der Hauptspeicher eines PCs besteht heutzutage vollständig aus synchronen, dynamischen RAM-Bausteinen (SDRAMs). Dynamische RAMs (Random Access Memory) besitzen Speicherzellen, die die Information als Ladungsträger in kleinen Kapazitäten (Kondensatoren) speichern. Der Lesezugriff auf eine Speicherzelle zerstört deren Inhalt, so dass dieser danach erneut eingeschrieben werden muss. Dieses Wiedereinschreiben wird von den Schreib-/Leseverstärkern im Baustein automatisch durchgeführt, sodass sich der Speicher-Controller nicht darum kümmern muss. Aber auch durch unvermeidliche Leckströme werden die Kondensatoren im Laufe der Zeit entladen<sup>19</sup>. Daher muss der Speicher-Controller die gesamte gespeicherte Information in regelmäßigen Abständen von wenigen Millisekunden (max. 64 ms) wieder auffrischen (Refresh), was durch Lesezugriffe auf alle Speicherzellen mit dem oben erwähnten automatischen Rückschreiben geschieht, ohne dass der gelesene Speicherinhalt aus dem Speicherbaustein herausgegeben wird.

Pufferregister

Der Zugriff auf den Speicher geschieht mit Hilfe eines Taktes, durch den die auszulesende Speicherzelle in ein Pufferregister geladen bzw. aus dem die eingeschriebene Information in die Speicherzelle gelangt. Das Pufferregister kann vom Controller erheblich schneller angesprochen werden (bis zu 800 MHz) als die Speicherzellen selbst (ca. 25 MHz). Wegen dieser Taktsteuerung spricht man von "synchronen Speichern".

DDR-RAM

Prefetch

Seit Anfang 2001 haben sich von den verschiedenen SDRAM-Bausteinen die DDR-SDRAMs, kurz: DDR-RAMs, im großen Umfang durchgesetzt. Ihr großer (namensgebender) Vorteil ist die Eigenschaft, mit jedem Zugriff vorausschauend gleich zwei nebeneinander liegende Speicherwörter aus einem internen Pufferregister zu laden (*Prefetch*) und diese dann in einer einzigen Taktperiode durch zwei Datentransfers zu lesen – je einen mit der positiven und der negativen Taktflanke. Beim Schreiben geht man analog vor, d.h. nachdem ein 64 Bit-Wort mit der ersten Taktflanke zwischengespeichert wurde, werden mit der fallenden Taktflanke ein zweites 64-Bit-Wort übertragen und beide Wörter gleichzeitig in den Speicher eingeschrieben. Zusammen mit einer zweikanaligen Ankopplung können pro Taktzyklus vier Datenwörter zwischen Prozessor und Speicher übertragen werden.<sup>20</sup>

DDR2

Bei der zweiten Generation der DDR-RAMs, dem DDR2, wurde die Anzahl der vorausschauend geladenen Speicherwörter auf vier erhöht, die dann in zwei Taktperioden mit vier Datentransfers aus dem internen Pufferregister gelesen werden. Der aktuelle Standard, DDR3, erhöht die Anzahl der simultan gelesenen Speicherwörter weiter auf 8, die in vier Taktperioden übertragen werden. Die beschriebene technologische Entwicklung machte eine Reduzierung der Betriebsspannung von 2,5 V bei DDR-RAMs über 1,8 V bei DDR2-RAMs auf 1,5

<sup>&</sup>lt;sup>19</sup>Man spricht deshalb von einem "flüchtigen" Speicher (volatile Memory).

<sup>&</sup>lt;sup>20</sup>Dieses Verfahren wird von Intel als *quad-pumped* bezeichnet.

V bei den DDR3-RAMs nötig und möglich. Momentan werden in PCs haupt- DDR3 sächlich DDR2- und DDR3-Speicherbausteine eingesetzt. Daher beschränken wir unsere weiteren Erläuterungen auf diese Bausteine. Auf ihre genauen Spezifikationen und Eigenschaften gehen wir in einem Unterabschnitt ein.

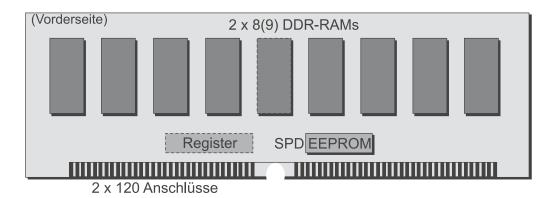

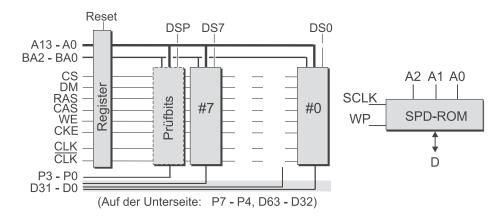

Durch die beschriebene Integration der DRAM-Speicher-Controller in die North Bridge des Chipsatzes bzw. in den Prozessorchip selbst wird einerseits der Aufbau der Speichermodule vereinfacht und kostengünstiger. Andererseits verlangen die großen Stückzahlen und die geforderte Kompatibilität eine gewisse Standardisierung der Module. In Abbildung 1.8 ist eine Platine mit einem DDR2/DDR3-DRAM-Speichermodul skizziert.

Abbildung 1.8: Der Aufbau eines DDR2/DDR3-Speichermoduls

Diese Platine ist ca. 133 x 30 mm<sup>2</sup> groß und wird in einem Steckplatz der Hauptplatine untergebracht. Dazu besitzt sie auf jeder ihrer Platinenseiten an der Unterkante eine Reihe von 120 Steckkontakten, die direkt in die Platinenoberfläche eingeätzt werden ("direkte Steckung"). <sup>21</sup> Die beidseitigen Steckkontakte geben dem Speichermodul die Bezeichnung DIMM (Dual Inline Memory Module). DIMMs werden in einseitig bestückte DIMMs (single-sided DIMMs) und zwei- DIMM seitig bestückte DIMMs (double-sided DIMMs) unterschieden, je nachdem, ob sie nur auf einer oder aber auf beiden Platinenseiten DRAM-Bausteine tragen. Leider bedingt der Aufbau eines DIMMs und seine Verbindung mit der Hauptplatine über einen Steckplatz eine Verzögerung der Signale zwischen Speicher und Speicher-Controller in der North Bridge. Daher erreichen DIMMs noch nicht die Ubertragungsraten, die man in speziellen Systemen (wie z.B. Spielecomputern oder Graphikkarten) durch direkt auf der Systemplatine eingelötete schnelle Speicherbausteine erhält.

Die DIMMs unterscheiden sich nun wesentlich darin, welche Speicherbausteine auf ihnen implementiert sind. Wie gesagt, kann es sich dabei um DDR2- oder DDR3-RAMs handeln. Auch die Kapazität der Bausteine kann variieren. So